# Intel® Atom™ Processor D2000 and N2000 Series

Datasheet – Volume 2 of 2

Refer to Doc ID 326136-002 for Volume 1 of 2

December 2011

Revision 002

Document Number: 326137-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel® 64 requires a computer system with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for Intel 64. Processor will not operate (including 32-bit operation) without an Intel 64-enabled BIOS. Performance will vary depending on your hardware and software configurations. See http://www.intel.com/technology/intel64/index.htm for more information including details on which processors support Intel 64, or consult with your system vendor for more information.

Hyper-Threading Technology requires a computer system with a processor supporting Hyper-Threading Technology and HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you see. See http://www.intel.com/technology/hypertheading/ for more information including details on which processor supports HT Technology.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Click here for details. See the Processor Spec Finder or contact your Intel representative for more information.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011 Intel Corporation. All rights reserved

### **Contents**

| 1 | Proces | sor Confi | guration Registers                                               | 16    |

|---|--------|-----------|------------------------------------------------------------------|-------|

|   | 1.1    | Related   | Documents                                                        | 16    |

|   | 1.2    |           | Terminology                                                      |       |

|   | 1.3    |           | Address Map                                                      |       |

|   | 1.4    |           | Atom™ Processor D2000 series and N2000 Series Address Spaces     |       |

|   |        | 1.4.1     | Physical Address Space                                           |       |

|   |        | 1.4.2     | System DRAM Address Space                                        |       |

|   |        | 1.4.3     | IO Space                                                         |       |

|   |        | 1.4.4     | PCI Config Space                                                 |       |

|   | 1.5    | Physical  | to DRAM Address Space Mapping                                    |       |

|   |        | 1.5.1     | Intel® Atom™ Processor D2000 series and N2000 Series Memory      |       |

|   |        | 1.0.1     | Mapping Registers                                                |       |

|   | 1.6    | Intel® A  | Atom™ Processor D2000 series and N2000 Series Memory Map         |       |

|   | 1.0    |           | Programming Examples                                             | 22    |

|   |        | 1.6.1     | Case 1: 2GB DRAM. Min 1 GB PCI MMIO                              |       |

|   | 1.7    |           | Device Memory Ranges                                             |       |

|   | 1.7    | 1.7.1     | Device 0 (0/0/0) Memory Map                                      |       |

|   |        | 1.7.1     | Device 2 (0/2/0) Memory Map                                      |       |

|   |        | 1.7.2     | Legacy Address Range                                             |       |

|   |        | 1.7.4     | Main Memory Address Range (1 MB - HMBOUND)                       |       |

|   |        | 1.7.5     | PCI* Memory Address Range (HMBOUND - 4 GB)                       |       |

|   |        | 1.7.6     | System Management Mode (SMM)                                     |       |

|   |        | 1.7.7     | Intel® Atom™ Processor D2000 series and N2000 Series Interna     |       |

|   |        |           | Enforcement of SMM Protection                                    |       |

|   |        | 1.7.8     | I/O Address Space                                                | 35    |

|   | 1.8    | IO (POR   | T IN/OUT) Space                                                  | 37    |

|   |        | 1.8.1     | IO (PORT IN/OUT) Space                                           | 37    |

|   |        | 1.8.2     | Fixed I/O Address Ranges                                         |       |

|   |        | 1.8.3     | Variable I/O (PORT) Address Blocks                               | 37    |

|   |        | 1.8.4     | IO Space registers                                               | 38    |

|   | 1.9    | MMIO S    | pace                                                             | 40    |

|   |        | 1.9.1     | MMIO Space                                                       | 40    |

|   |        | 1.9.2     | MMIO Space Registers                                             | 40    |

|   | 1.10   | IOSF-SE   | B (Msg Bus) Space                                                | 70    |

|   |        | 1.10.1    | Intel® Atom™ Processor D2000 series and N2000 Series IOSF-S      | В     |

|   |        |           | Bus Access                                                       |       |

|   |        | 1.10.2    | Intel® Atom™ Processor D2000 series and N2000 Series IOSF-S      | В     |

|   |        |           | Access mechanisms                                                |       |

|   |        | 1.10.3    | Intel® Atom™ Processor D2000 series and N2000 Series IOSF-S      |       |

|   |        |           | Port Assignments                                                 |       |

|   |        | 1.10.4    | Msg Bus Register Space                                           |       |

|   | 1.11   |           | Atom™ Processor D2000 series and N2000 Series Full Register List |       |

|   |        | 1.11.1    | AEC                                                              |       |

|   |        | 1.11.2    | BEMONO                                                           |       |

|   |        | 1.11.3    | BEMON1                                                           |       |

|   |        | 1.11.4    | BEMON2                                                           |       |

|   |        | 1.11.5    | BEMON3                                                           |       |

|   |        | 1.11.6    | BIST HEADER TYPE AND MASTER LATENCY TIMER CACHELINE              | : 142 |

| 1.11.7  | CLASS_CODE_AND_REVISION_ID              | 143  |

|---------|-----------------------------------------|------|

| 1.11.8  | ID                                      |      |

| 1.11.9  | MANUFACTURING_ID                        |      |

| 1.11.10 | MESSAGESIDEBAND_DATA_REGISTER           |      |

| 1.11.10 | MESSAGE_CONTROLSIDEBAND_PACKET_REGISTER | 1/1/ |

|         | PCI_STATUS_AND_PCI_COMMAND              | 144  |

|         | SCRATCHPAD_REGISTER                     |      |

|         | SIDEBAND_PACKET_REGISTER_EXTENSION      |      |

|         |                                         |      |

| 1.11.15 | SSID                                    | 145  |

|         | DFX.GMCH_PERF_CAPABILITIES              |      |

|         | DFX.GMCH_PERF_EVTSEL0                   |      |

|         | DFX.GMCH_PERF_EVTSEL1                   |      |

| 1.11.19 |                                         |      |

| 1.11.20 | <b>=</b>                                |      |

| 1.11.21 | DFX.GMCH_PERF_FIXED_CTR0                |      |

| 1.11.22 |                                         |      |

|         | DFX.GMCH_PERF_GLOBAL_CTRL               |      |

| 1.11.24 | DFX.GMCH_PERF_GLOBAL_OVF_CTRL           | 149  |

| 1.11.25 | DFX.GMCH_PERF_GLOBAL_STATUS             | 150  |

| 1.11.26 | DFX.GMCH_PERF_GP_CTRO_H                 | 150  |

| 1.11.27 | DFX.GMCH_PERF_GP_CTRO_L                 | 151  |

| 1.11.28 | DFX.GMCH_PERF_GP_CTR1_H                 | 151  |

| 1.11.29 | DFX.GMCH_PERF_GP_CTR1_L                 | 151  |

|         | DFX.GMCH_PERF_GP_CTR2_H                 |      |

| 1.11.31 | DFX.GMCH_PERF_GP_CTR2_L                 | 152  |

| 1.11.32 |                                         |      |

| 1.11.33 | DFX.GMCH_PERF_GP_CTR3_L                 |      |

| 1.11.34 | DISPLAY_CONTROLLER.ADPA                 |      |

| 1.11.35 | DISPLAY_CONTROLLER.AUD_CNTL_ST          |      |

|         | DISPLAY_CONTROLLER.AUD_CONFIG           | 156  |

| 1.11.37 |                                         |      |

| 1.11.38 | DISPLAY_CONTROLLER.AUD_CTS_ENABLE       |      |

| 1.11.39 |                                         |      |

| 1.11.40 | DISPLAY_CONTROLLER.AUD_FUNCGRP_SUBN_CNT | 158  |

| 1.11.41 | DISPLAY_CONTROLLER.AUD_FUNC_GRP         |      |

| 1.11.42 | DISPLAY_CONTROLLER.AUD_GRP_CAP          |      |

| 1.11.43 | DISPLAY_CONTROLLER.AUD_HDMIW_HDMIEDID   |      |

| 1.11.44 | DISPLAY_CONTROLLER.AUD_HDMIW_INFOFR     |      |

| 1.11.45 | DISPLAY_CONTROLLER.AUD_HDMIW_STATUS     |      |

| 1.11.46 | DISPLAY_CONTROLLER.AUD_OUT_CH_STR       |      |

| 1.11.47 | DISPLAY_CONTROLLER.AUD_OUT_CWCAP        |      |

|         | DISPLAY_CONTROLLER.AUD_OUT_DIG_CNVT     |      |

| 1.11.49 | DISPLAY_CONTROLLER.AUD_OUT_PCMSIZE      |      |

| 1.11.50 | DISPLAY_CONTROLLER.AUD_OUT_STR          |      |

| 1.11.51 | DISPLAY_CONTROLLER.AUD_OUT_STR_DESC     | 166  |

| 1.11.52 | DISPLAY_CONTROLLER.AUD_PINW_CAP         | 160  |

| 1.11.53 | DISPLAY_CONTROLLER.AUD_PINW_CNTR        |      |

| 1.11.54 | DISPLAY_CONTROLLER.AUD_PINW_CONFIG      |      |

| 1.11.54 | DISPLAY_CONTROLLER.AUD_PINW_CONNLNG     |      |

|         | DISPLAY_CONTROLLER.AUD_PINW_CONNLST     |      |

| 1.11.56 |                                         |      |

| 1.11.57 | DISPLAY_CONTROLLER_AUD_PINW_UNSOLRESP   |      |

| 1.11.58 | DISPLAY_CONTROLLER_AUD_PIN_CAP          |      |

| 1.11.59 | DISPLAY_CONTROLLER_AUD_PWRST            |      |

| 1.11.60 | DISPLAY_CONTROLLER_AUD_RID              |      |

| 1.11.61 | DISPLAY_CONTROLLER AUD_SID              |      |

| 1116)   | DISPLAY CONTROLLER ALID SID             | 174  |

| 1.11.63 | DISPLAY_CONTROLLER.AUD_SUPPWR        | 174 |

|---------|--------------------------------------|-----|

| 1.11.64 | DISPLAY_CONTROLLER.AUD_VID_DID       | 175 |

| 1.11.65 | DISPLAY_CONTROLLER.BCLRPAT_A         | 175 |

|         | DISPLAY_CONTROLLER.BCLRPAT_B         |     |

|         | DISPLAY_CONTROLLER.BLC_PWM_CLT2      |     |

| 1.11.68 | DISPLAY_CONTROLLER.BLC_PWM_CTL       | 177 |

|         | DISPLAY_CONTROLLER.BLM_HIST_CTL      |     |

|         | DISPLAY_CONTROLLER.CBR1              |     |

|         | DISPLAY_CONTROLLER.CBR2              |     |

|         | DISPLAY_CONTROLLER.CBR3              |     |

|         | DISPLAY_CONTROLLER.CCBR              |     |

|         | DISPLAY_CONTROLLER.CRCCTRLALPHAA     |     |

|         | DISPLAY_CONTROLLER.CRCCTRLALPHAB     |     |

|         | DISPLAY_CONTROLLER.CRCCTRLBLUEA      |     |

|         | DISPLAY_CONTROLLER.CRCCTRLBLUEB      |     |

|         | DISPLAY_CONTROLLER.CRCCTRLGREENA     |     |

|         | DISPLAY_CONTROLLER.CRCCTRLGREENB     |     |

|         | DISPLAY_CONTROLLER.CRCCTRLREDA       |     |

| 1.11.81 | DISPLAY CONTROLLER.CRCCTRLREDB       |     |

|         | DISPLAY_CONTROLLER.CRCCTRLRESIDUE2A  |     |

|         | DISPLAY_CONTROLLER.CRCCTRLRESIDUE2B  |     |

|         | DISPLAY_CONTROLLER.CRCRESALPHAA      |     |

|         | DISPLAY_CONTROLLER.CRCRESALPHAB      |     |

|         | DISPLAY_CONTROLLER.CRCRESBLUEA       |     |

|         | DISPLAY_CONTROLLER.CRCRESBLUEB       |     |

|         | DISPLAY_CONTROLLER.CRCRESGREENA      |     |

| 1.11.89 |                                      |     |

|         | DISPLAY_CONTROLLER.CRCRESREDA        |     |

| 1.11.91 | DISPLAY_CONTROLLER.CRCRESREDB        |     |

|         | DISPLAY_CONTROLLER.CRCRESRESIDUAL2B  |     |

|         | DISPLAY_CONTROLLER.CRCRESRESIDUE2A   |     |

|         | DISPLAY_CONTROLLER.CRTIO_DFX         |     |

|         | DISPLAY_CONTROLLER.CURABASE          |     |

|         | DISPLAY_CONTROLLER.CURACNTR          |     |

|         | DISPLAY_CONTROLLER.CURAPALET         |     |

|         | DISPLAY_CONTROLLER.CURAPOS           |     |

|         | DISPLAY_CONTROLLER.CURARESV          |     |

|         | DISPLAY_CONTROLLER.CURBBASE          |     |

|         | DISPLAY_CONTROLLER.CURBCNTR          |     |

|         | DISPLAY_CONTROLLER.CURBPOS           |     |

|         | BDISPLAY_CONTROLLER.CURBRESV         |     |

|         | DISPLAY_CONTROLLER.CURB_PALET        |     |

|         | DISPLAY_CONTROLLER.DCLRC0            |     |

|         | DISPLAY_CONTROLLER.DCLRC1            |     |

|         | DISPLAY_CONTROLLER.DCLRKM            |     |

|         | BDISPLAY_CONTROLLER.DCLRKV           |     |

|         | DISPLAY_CONTROLLER.DOVSTA            |     |

|         | DISPLAY_CONTROLLER.DOVSTAEX          |     |

|         | DISPLAY_CONTROLLER.DOVSTALX          |     |

|         | DISPLAY_CONTROLLER.DPALETTE_B        |     |

|         | BDISPLAY_CONTROLLER.DPB_AUX_CH_CTL   |     |

|         | IDISPLAY_CONTROLLER.DPB_AUX_CH_DATA1 |     |

|         | DISPLAY_CONTROLLER.DPB_AUX_CH_DATA1  |     |

|         | DISPLAY_CONTROLLER.DPB_AUX_CH_DATA2  |     |

|         | DISPLAY_CONTROLLER.DPB_AUX_CH_DATAS  |     |

|         | DISPLAY_CONTROLLER.DPD_AUX_CH_DATA4  |     |

6

| 1.11.119 DISPLAY_CONTROLLER.DPC                  |     |

|--------------------------------------------------|-----|

| 1.11.120 DISPLAY_CONTROLLER.DPC_AUX_CH_CTL       | 210 |

| 1.11.121 DISPLAY_CONTROLLER.DPC_AUX_CH_DATA1     | 212 |

| 1.11.122 DISPLAY_CONTROLLER.DPC_AUX_CH_DATA2     | 212 |

| 1.11.123 DISPLAY_CONTROLLER.DPC_AUX_CH_DATA3     |     |

| 1.11.124 DISPLAY_CONTROLLER.DPC_AUX_CH_DATA4     |     |

| 1.11.125 DISPLAY_CONTROLLER.DPC_AUX_CH_DATA5     | 213 |

| 1.11.126 DISPLAY_CONTROLLER.DPIO_DATA_REGISTER   | 214 |

| 1.11.127 DISPLAY_CONTROLLER.DPIO_PACKET_REGISTER | 214 |

| 1.11.128 DISPLAY_CONTROLLER.DPLLAMD              | 214 |

| 1.11.129 DISPLAY_CONTROLLER.DPLLA_CTRL           | 215 |

| 1.11.130 DISPLAY_CONTROLLER.DPLLBMD              | 217 |

| 1.11.131 DISPLAY_CONTROLLER.DPLLB_CTRL           | 217 |

| 1.11.132 DISPLAY_CONTROLLER.DP_AUX_CH_AKSV_HI    | 219 |

| 1.11.133 DISPLAY_CONTROLLER.DP_AUX_CH_AKSV_LO    | 220 |

| 1.11.134 DISPLAY_CONTROLLER.DP_B                 |     |

| 1.11.135 DISPLAY_CONTROLLER.DSPAADDR             |     |

| 1.11.136 DISPLAY_CONTROLLER.DSPACNTR             | 222 |

| 1.11.137 DISPLAY_CONTROLLER.DSPAKEYMSK           | 224 |

| 1.11.138 DISPLAY_CONTROLLER.DSPAKEYVAL           | 225 |

| 1.11.139 DISPLAY_CONTROLLER.DSPALINOFF           |     |

| 1.11.140 DISPLAY_CONTROLLER.DSPARB               |     |

| 1.11.141 DISPLAY_CONTROLLER.DSPASTRIDE           |     |

| 1.11.142 DISPLAY_CONTROLLER.DSPASURF             |     |

| 1.11.143 DISPLAY_CONTROLLER.DSPASURFLIVE         |     |

| 1.11.144 DISPLAY_CONTROLLER.DSPATILEOFF          |     |

| 1.11.145 DISPLAY_CONTROLLER.DSPBADDR             |     |

| 1.11.146 DISPLAY_CONTROLLER.DSPBCNTR             |     |

| 1.11.147 DISPLAY_CONTROLLER.DSPBFLPQSTAT         |     |

| 1.11.148 DISPLAY_CONTROLLER.DSPBKEYMSK           |     |

| 1.11.149 DISPLAY_CONTROLLER.DSPBKEYVAL           |     |

| 1.11.150 DISPLAY_CONTROLLER.DSPBLINOFFSET        |     |

| 1.11.151 DISPLAY_CONTROLLER.DSPBSTRIDE           |     |

| 1.11.152 DISPLAY_CONTROLLER.DSPBSURF             |     |

| 1.11.153 DISPLAY_CONTROLLER.DSPBSURFLIVE         |     |

| 1.11.154 DISPLAY_CONTROLLER.DSPBTILEOFF          |     |

| 1.11.155 DISPLAY_CONTROLLER.DSPCCNTR             |     |

| 1.11.156 DISPLAY_CONTROLLER.DSPCCONTALPHA        |     |

| 1.11.157 DISPLAY_CONTROLLER.DSPCKEYMAXVAL        |     |

| 1.11.158 DISPLAY_CONTROLLER.DSPCKEYMINVAL        |     |

| 1.11.159 DISPLAY_CONTROLLER.DSPCKEYMSK           |     |

| 1.11.160 DISPLAY_CONTROLLER.DSPCLINOFF           |     |

| 1.11.161 DISPLAY_CONTROLLER.DSPCLK_GATE_D        |     |

| 1.11.162 DISPLAY_CONTROLLER.DSPCPOS              |     |

| 1.11.163 DISPLAY_CONTROLLER.DSPCSIZE             |     |

| 1.11.164 DISPLAY_CONTROLLER.DSPCSTRIDE           |     |

| 1.11.165 DISPLAY_CONTROLLER.DSPCSURF             |     |

| 1.11.166 DISPLAY_CONTROLLER.DSPCTILEOFF          |     |

| 1.11.167 DISPLAY_CONTROLLER.DWINPOS              |     |

| 1.11.168 DISPLAY_CONTROLLER.DWINSZ               |     |

| 1.11.169 DISPLAY_CONTROLLER.D_STATE              |     |

| 1.11.170 DISPLAY_CONTROLLER.FW1                  |     |

| 1.11.171 DISPLAY_CONTROLLER.FW2                  |     |

| 1.11.172 DISPLAY_CONTROLLER.FW3                  |     |

| 1.11.173 DISPLAY_CONTROLLER.FW4                  |     |

| 1 11 174 DISDI AV CONTROLLED EME                 |     |

| 1.11.175 DISPLAY_CONTROLLER.FW6               |       |

|-----------------------------------------------|-------|

| 1.11.176 DISPLAY_CONTROLLER.GAMC0             |       |

| 1.11.177 DISPLAY_CONTROLLER.GAMC1             | . 251 |

| 1.11.178 DISPLAY_CONTROLLER.GAMC2             |       |

| 1.11.179 DISPLAY_CONTROLLER.GAMC3             | . 251 |

| 1.11.180 DISPLAY_CONTROLLER.GAMC4             |       |

| 1.11.181 DISPLAY_CONTROLLER.GAMC5             |       |

| 1.11.182 DISPLAY_CONTROLLER.GMBUS0            |       |

| 1.11.183 DISPLAY_CONTROLLER.GMBUS1            |       |

| 1.11.184 DISPLAY_CONTROLLER.GMBUS2            |       |

| 1.11.185 DISPLAY CONTROLLER.GMBUS3            |       |

| 1.11.186 DISPLAY_CONTROLLER.GMBUS4            |       |

|                                               |       |

| 1.11.187 DISPLAY_CONTROLLER.GMBUS5            |       |

| 1.11.188 DISPLAY_CONTROLLER.GMBUS6            |       |

| 1.11.189 DISPLAY_CONTROLLER.GMBUS7            |       |

| 1.11.190 DISPLAY_CONTROLLER.GPIOCTL_0         | . 259 |

| 1.11.191 DISPLAY_CONTROLLER.GPIOCTL_1         | . 261 |

| 1.11.192 DISPLAY_CONTROLLER.GPIOCTL_2         |       |

| 1.11.193 DISPLAY_CONTROLLER.GPIOCTL_3         |       |

| 1.11.194 DISPLAY_CONTROLLER.GPIOCTL_4         | 266   |

| 1.11.195 DISPLAY_CONTROLLER.HBLANK_A          | 269   |

| 1.11.196 DISPLAY_CONTROLLER.HBLANK_           |       |

| BPIPE B HORIZONTAL BLANK REGISTER             | 269   |

| 1.11.197 DISPLAY_CONTROLLER.HDCP_AKEY_HI      |       |

| 1.11.198 DISPLAY_CONTROLLER.HDCP_AKEY_LO      |       |

| 1.11.199 DISPLAY_CONTROLLER.HDCP_AKEY_MED     |       |

| 1.11.200 DISPLAY_CONTROLLER.HDCP_AKSV_HI      | 271   |

| 1.11.201 DISPLAY_CONTROLLER.HDCP_AKSV_LO      |       |

| 1.11.202 DISPLAY_CONTROLLER.HDCP_AN_HI        |       |

|                                               |       |

| 1.11.203 DISPLAY_CONTROLLER.HDCP_AN_LO        |       |

| 1.11.204 DISPLAY_CONTROLLER.HDCP_BKSV_HI      | . 212 |

| 1.11.205 DISPLAY_CONTROLLER.HDCP_BKSV_LO      |       |

| 1.11.206 DISPLAY_CONTROLLER.HDCP_CONFIG       |       |

| 1.11.207 DISPLAY_CONTROLLER.HDCP_DBG_STAT     |       |

| 1.11.208 DISPLAY_CONTROLLER.HDCP_INIT         |       |

| 1.11.209 DISPLAY_CONTROLLER.HDCP_REP          | . 274 |

| 1.11.210 DISPLAY_CONTROLLER.HDCP_RI           | . 274 |

| 1.11.211 DISPLAY_CONTROLLER.HDCP_SHA1_IN      |       |

| 1.11.212 DISPLAY_CONTROLLER.HDCP_STATUS       | 275   |

| 1.11.213 DISPLAY_CONTROLLER.HDCP_V_0          | . 276 |

| 1.11.214 DISPLAY_CONTROLLER.HDCP_V_1          | . 276 |

| 1.11.215 DISPLAY_CONTROLLER.HDCP_V_2          | . 276 |

| 1.11.216 DISPLAY_CONTROLLER.HDCP_V_3          | . 277 |

| 1.11.217 DISPLAY_CONTROLLER.HDCP_V_4          |       |

| 1.11.218 DISPLAY_CONTROLLER.HISTOGRAM_        |       |

| THRESHOLD_GUARDBAND_REGISTER                  | 277   |

| 1.11.219 DISPLAY_CONTROLLER.HORZ_PH           |       |

| 1.11.220 DISPLAY_CONTROLLER.HSYNC_A           |       |

| 1.11.221 DISPLAY_CONTROLLER.HSYNC_BPIPE       | 210   |

| _B_HORIZONTAL_SYNC_REGISTER                   | 270   |

|                                               |       |

| 1.11.222 DISPLAY_CONTROLLER.HTOTAL_A          | . 219 |

| 1.11.223 DISPLAY_CONTROLLER.HTOTAL_BPIPE      | 202   |

| _B_HORIZONTAL_TOTAL_REGISTER                  | . 280 |

| 1.11.224 DISPLAY_CONTROLLER.IMAGE_ENHANCEMENT | 000   |

| _BIN_DATA_REGISTER                            | 280   |

| 1.11.225 DISPLAY_CONTROLLER.INIT_PHS          | . 280 |

|   | 1.11.226 DISPLAY_CONTROLLER.LVDS            |     |

|---|---------------------------------------------|-----|

| 1 | 1.11.227 DISPLAY_CONTROLLER.LVDSCKT1        | 284 |

| 1 | 1.11.228 DISPLAY_CONTROLLER.LVDSCKT2        | 284 |

| 1 | 1.11.229 DISPLAY_CONTROLLER.LVDSCKT3        | 285 |

| 1 | 1.11.230 DISPLAY_CONTROLLER.LVDSCKT4        | 285 |

| 1 | 1.11.231 DISPLAY_CONTROLLER.LVDSTCR         | 286 |

| 1 | 1.11.232 DISPLAY_CONTROLLER.OBUF_OU         | 286 |

| 1 | 1.11.233 DISPLAY_CONTROLLER.OBUF_OV         | 287 |

| 1 | 1.11.234 DISPLAY_CONTROLLER.OBUF_OY         | 287 |

| 1 | 1.11.235 DISPLAY_CONTROLLER.OBUF_1U         | 288 |

| 1 | 1.11.236 DISPLAY_CONTROLLER.OBUF_1V         | 288 |

| 1 | 1.11.237 DISPLAY_CONTROLLER.OBUF_1Y         | 289 |

| 1 | 1.11.238 DISPLAY_CONTROLLER.OCLRC0          | 289 |

| 1 | 1.11.239 DISPLAY_CONTROLLER.OCLRC1          | 290 |

| 1 | 1.11.240 DISPLAY_CONTROLLER.OCOMD           | 291 |

|   | 1.11.241 DISPLAY_CONTROLLER.OCONFIG         |     |

|   | 1.11.242 DISPLAY_CONTROLLER.OGAMCO          |     |

|   | 1.11.243 DISPLAY_CONTROLLER.OGAMC1          |     |

| 1 | 1.11.244 DISPLAY_CONTROLLER.OGAMC2          | 296 |

| 1 | 1.11.245 DISPLAY_CONTROLLER.OGAMC3          | 296 |

|   | 1.11.246 DISPLAY_CONTROLLER.OGAMC4          |     |

|   | 1.11.247 DISPLAY_CONTROLLER.OGAMC5          |     |

|   | 1.11.248 DISPLAY_CONTROLLER.OSTART_OU       |     |

|   | 1.11.249 DISPLAY_CONTROLLER.OSTART_OV       |     |

|   | 1.11.250 DISPLAY_CONTROLLER.OSTART_0Y       |     |

|   | 1.11.251 DISPLAY_CONTROLLER.OSTART_1U       |     |

| 1 | 1.11.252 DISPLAY_CONTROLLER.OSTART_1V       | 300 |

|   | 1.11.253 DISPLAY_CONTROLLER.OSTART_1Y       |     |

|   | 1.11.254 DISPLAY_CONTROLLER.OSTRIDE         |     |

|   | 1.11.255 DISPLAY_CONTROLLER.OTEST           |     |

|   | 1.11.256 DISPLAY_CONTROLLER.OTILEOFF_OU     |     |

|   | 1.11.257 DISPLAY_CONTROLLER.OTILEOFF_OV     |     |

|   | 1.11.258 DISPLAY_CONTROLLER.OTILEOFF_OY     |     |

|   | 1.11.259 DISPLAY_CONTROLLER.OTILEOFF_1U     |     |

|   | 1.11.260 DISPLAY_CONTROLLER.OTILEOFF_1V     |     |

|   | 1.11.261 DISPLAY_CONTROLLER.OTILEOFF_1Y     |     |

|   | 1.11.262 DISPLAY_CONTROLLER.OVADD           |     |

|   | 1.11.263 DISPLAY_CONTROLLER.OVRSYNCPH0      |     |

|   | 1.11.264 DISPLAY_CONTROLLER.OVRSYNCPH1      |     |

|   | 1.11.265 DISPLAY_CONTROLLER.OVRSYNCPH2      |     |

|   | 1.11.266 DISPLAY_CONTROLLER.OVRSYNCPH3      |     |

|   | 1.11.267 DISPLAY_CONTROLLER.PFIT_CONTROL    |     |

|   | 1.11.268 DISPLAY_CONTROLLER.PFIT_PGM_RATIOS |     |

|   | 1.11.269 DISPLAY_CONTROLLER.PIPEACONF       |     |

|   | 1.11.270 DISPLAY_CONTROLLER.PIPEADPLINKM    |     |

|   | 1.11.271 DISPLAY_CONTROLLER.PIPEADPLINKN    |     |

|   | 1.11.272 DISPLAY_CONTROLLER.PIPEAFRAMEHIGH  |     |

|   | 1.11.273 DISPLAY_CONTROLLER.PIPEAFRAMEPIXEL |     |

|   | 1.11.274 DISPLAY_CONTROLLER.PIPEAGCMAXBLUE  |     |

|   | 1.11.275 DISPLAY_CONTROLLER.PIPEAGCMAXGREEN |     |

|   | 1.11.276 DISPLAY_CONTROLLER.PIPEAGCMAXRED   |     |

|   | 1.11.277 DISPLAY_CONTROLLER.PIPEAGMCHDATAM  |     |

|   | 1.11.278 DISPLAY_CONTROLLER.PIPEAGMCHDATAN  |     |

|   | 1.11.279 DISPLAY_CONTROLLER.PIPEASTAT       |     |

|   | 1.11.280 DISPLAY_CONTROLLER.PIPEA_DSL       |     |

|   | 1 11 201 DISDLAY CONTROLLED DIDEA SIC       |     |

| 1.11.282 DISPLAY_CONTROLLER.PIPEBCONF                  |               |

|--------------------------------------------------------|---------------|

| 1.11.283 DISPLAY_CONTROLLER.PIPEBDPLINKM               | 321           |

| 1.11.284 DISPLAY_CONTROLLER.PIPEBDPLINKN               | 321           |

| 1.11.285 DISPLAY CONTROLLER.PIPEBFRAMEHIGH             |               |

| 1.11.286 DISPLAY_CONTROLLER.PIPEBFRAMEPIXEL            | 323           |

| 1.11.287 DISPLAY_CONTROLLER.PIPEBGCMAXBLUE             |               |

| 1.11.288 DISPLAY_CONTROLLER.PIPEBGCMAXGREEN            |               |

| 1.11.289 DISPLAY_CONTROLLER.PIPEBGCMAXRED              |               |

| 1.11.290 DISPLAY_CONTROLLER.PIPEBGMCHDATAM             |               |

| 1.11.291 DISPLAY_CONTROLLER.PIPEBGMCHDATAN             |               |

| 1.11.292 DISPLAY_CONTROLLER.PIPEBSRC                   |               |

| 1.11.293 DISPLAY_CONTROLLER.PIPEBSTAT                  |               |

| 1.11.294 DISPLAY_CONTROLLER.PIPEB_DSLDISPLAY_SCAN_LINE |               |

| 1.11.295 DISPLAY_CONTROLLER.PIPEB_SLC                  |               |

| 1.11.296 DISPLAY_CONTROLLER.PIPESRCA                   |               |

| 1.11.297 DISPLAY_CONTROLLER.PORT_HOTPLUG_EN            |               |

| 1.11.298 DISPLAY_CONTROLLER.PORT_HOTPLUG_STAT          |               |

| 1.11.299 DISPLAY_CONTROLLER.PP_CONTROL                 |               |

| 1.11.300 DISPLAY_CONTROLLER.PP_DIVISOR                 |               |

| 1.11.301 DISPLAY_CONTROLLER.PP_OFF_DELAYS              |               |

| 1.11.302 DISPLAY_CONTROLLER.PP_ON_DELAYS               |               |

| 1.11.303 DISPLAY_CONTROLLER.PP_STATUS                  |               |

| 1.11.304 DISPLAY_CONTROLLER.RAMCLK_GATE_D              |               |

| 1.11.305 DISPLAY_CONTROLLER.RESERVED                   |               |

| 1.11.306                                               | 342           |

| DISPLAY_CONTROLLER.RESERVED_USED_TO_BE_AUTO_SCALING    | DATIOS DEADE  |

| 1.11.307                                               | _KATIOS_KEADI |

| DISPLAY_CONTROLLER.RESERVED_USED_TO_BE_SCALING_INITI   | VI DUVCE 343  |

| 1.11.308 DISPLAY_CONTROLLER.SCHRKEN                    |               |

| 1.11.309 DISPLAY_CONTROLLER.SCHRKVH                    |               |

| 1.11.310 DISPLAY_CONTROLLER.SCHRKVL                    |               |

| 1.11.311 DISPLAY_CONTROLLER.SDVO_DP                    |               |

| 1.11.312 DISPLAY_CONTROLLER.SDVO_DP2                   |               |

| 1.11.313 DISPLAY_CONTROLLER.SDVO_HDMIB                 |               |

| 1.11.314 DISPLAY_CONTROLLER.SDVO_HDMIC                 |               |

| 1.11.315 DISPLAY_CONTROLLER.SHEIGHT                    |               |

| 1.11.316 DISPLAY_CONTROLLER.SWFXX                      |               |

| 1.11.317 DISPLAY_CONTROLLER.SWIDTH                     |               |

| 1.11.318 DISPLAY_CONTROLLER.SWIDTHSW                   |               |

| 1.11.318DISPLAY_CONTROLLER.SWIDTHSW                    |               |

| 1.11.320 DISPLAY_CONTROLLER.UVSCALEV                   |               |

| 1.11.320DISPLAY_CONTROLLER.UV_HCOEFS                   |               |

|                                                        |               |

| 1.11.322 DISPLAY_CONTROLLER.UV_VCOEFS                  |               |

| 1.11.323 DISPLAY_CONTROLLER.UV_VPH                     |               |

| <u>=</u>                                               | 360           |

| 1.11.325 DISPLAY_CONTROLLER.VBLANK_                    | 2/0           |

| BPIPE_BVERTICAL_BLANK_REGISTER                         |               |

| 1.11.326 DISPLAY_CONTROLLER.VGACNTRL                   |               |

| 1.11.327 DISPLAY_CONTROLLER.VIDEO_DIP_CTL              |               |

| 1.11.328 DISPLAY_CONTROLLER.VIDEO_DIP_DATA             |               |

| 1.11.329 DISPLAY_CONTROLLER.VSYNCSHIFT_A               |               |

| 1.11.330 DISPLAY_CONTROLLER.VSYNCSHIFT_B               |               |

| 1.11.331 DISPLAY_CONTROLLER.VSYNC_A                    | 300           |

| 1.11.332                                               | TED 2/7       |

| DISPLAY_CONTROLLER.VSYNC_BPIPE_B_VERTICAL_SYNC_REGIS   |               |

| 1.11.333 DISPLAY_CONTROLLER.VTOTAL_A                   | 30/           |

| 1.11.334 DISPLAY_CONTROLLER.VTOTAL_                                  |             |

|----------------------------------------------------------------------|-------------|

| BPIPE_BVERTICAL_TOTAL_REGISTER                                       | 368         |

| 1.11.335 DISPLAY_CONTROLLER.YRGBSCALE                                | 368         |

| 1.11.336 DISPLAY_CONTROLLER.YRGB_VPH                                 | 369         |

| 1.11.337 DISPLAY_CONTROLLER.Y_HCOEFS                                 |             |

| 1.11.338 DISPLAY_CONTROLLER.Y_VCOEFS                                 |             |

| 1.11.339 DMI.AERECH_0_0_0_DMIBAR                                     |             |

| 1.11.340 DMI.AFERTMG_0_1_0_MMR                                       |             |

| 1.11.341 DMI.BGFCTL1_0_0_0_DMIBAR                                    |             |

| 1.11.342 DMI.BGFCTL2_0_0_0_DMIBAR                                    |             |

| 1.11.343 DMI.BGFCTL3_0_0_0_DMIBAR                                    |             |

| 1.11.344 DMI.BGFCTL4_0_0_0_DMIBAR                                    |             |

| 1.11.345 DMI.CAPIDO_ACMN_O_1_O_MMR                                   |             |

| 1.11.346 DMI.CAPIDO_B_O_1_O_MMR                                      |             |

| 1.11.347 DMI.CCCR_0_0_0_DMIBAR                                       |             |

| 1.11.348 DMI.CCRPR_0_0_0_DMIBAR                                      |             |

| 1.11.349 DMI.CCWPR_0_0_DMIBAR                                        |             |

| 1.11.350 DMI.CFG2_0_1_0_MMR                                          |             |

| 1.11.351 DMI.CFG3_0_0_0_DMIBAR                                       |             |

| 1.11.352 DMI.CFG4_0_0_0_DMIBAR                                       |             |

| 1.11.353 DMI.CFG_0_1_0_MMR                                           |             |

| 1.11.354 DMI.CMMPC_0_1_0_MMR                                         |             |

| 1.11.355 DMI.CMMSB_0_1_0_MMR                                         |             |

| 1.11.356 DMI.DEBUGPL1_0_1_0_PCI                                      |             |

| 1.11.357 DMI.DEBUGPLU_0_1_0_PCI                                      |             |

| 1.11.358 DMI.DEBUGPL_0_0_0_DMIBAR                                    |             |

| 1.11.359 DMI.DEBUGTLLL1_0_0_0_DMIBAR                                 |             |

| 1.11.360 DMI.DEBUGTLLL_0_0_0_DMIBAR                                  |             |

| 1.11.361 DMI.DEBUP3_0_0_0_DMIBAR<br>1.11.362 DMI.DMIATM_0_0_0_DMIBAR |             |

| 1.11.363 DMI.DMICC_0_0_0_DMIBAR                                      |             |

| 1.11.364 DMI.DMICEMSK_0_0_DMIBAR                                     |             |

| 1.11.365 DMI.DMICESTS_0_0_0_DMIBAR                                   |             |

| 1.11.366 DMI.DMIESD_0_0_0_DMIBAR                                     |             |

| 1.11.367 DMI.DMIETVM_0_0_0_DMIBAR                                    |             |

| 1.11.368 DMI.DMIPVCCAP1_0_0_0_DMIBAR                                 |             |

| 1.11.369 DMI.DMIPVCCAP2_0_0_DMIBAR                                   |             |

| 1.11.370 DMI.DMIPVCCTL_0_0_0_DMIBAR                                  |             |

| 1.11.371 DMI.DMIRCILCECH_0_0_0_DMIBAR                                |             |

| 1.11.372 DMI.DMIRCLDECH_0_0_0_DMIBAR                                 |             |

| 1.11.373 DMI.DMISSTSU_0_0_0_DMIBAR                                   |             |

| 1.11.374 DMI.DMISSTS_0_0_0_DMIBAR                                    |             |

| 1.11.375 DMI.DMISTS_0_0_0_DMIBAR                                     |             |

| 1.11.376 DMI.DMITC_0_0_0_DMIBAR                                      |             |

| 1.11.377 DMI.DMIUEMSK_0_0_0_DMIBAR                                   |             |

| 1.11.378 DMI.DMIUESEV_0_0_0_DMIBAR                                   |             |

| 1.11.379 DMI.DMIUESTS_0_0_0_DMIBAR                                   |             |

| 1.11.380 DMI.DMIVCOCCC_0_0_DMIBAR                                    |             |

| 1.11.381 DMI.DMIVCOCCL_0_0_0_DMIBAR                                  | 410         |

| 1.11.382 DMI.DMIVCONPRCA_0_0_0_DMIBAR                                | 410         |

| 1.11.383 DMI.DMIVCONPRCC_0_0_DMIBAR                                  |             |

| 1.11.384 DMI.DMIVCONPRCL_O_O_O_DMIBAR                                |             |

| 1.11.385 DMI.DMIVCOPRCA_0_0_DMIBAR                                   |             |

| 1.11.386 DMI.DMIVCOPRCC_0_0_0_DMIBAR                                 | 414         |

| 1.11.387 DMI.DMIVCOPRCL_0_0_0_DMIBAR                                 | 414         |

| 1 11 388 DMI DMIVCORCAP O O DMIRAR                                   | <b>∆</b> 15 |

| 1.11.389 DMI.DMIVCORCTL_0_0_0_DMIBAR     |       |

|------------------------------------------|-------|

| 1.11.390 DMI.DMIVCORSTS_0_0_0_DMIBAR     |       |

| 1.11.391 DMI.DMIVC1NPRCA_0_0_DMIBAR      |       |

| 1.11.392 DMI.DMIVC1PRCA_0_0_0_DMIBAR     |       |

| 1.11.393 DMI.DMIVC1RCAP_0_0_0_DMIBAR     |       |

| 1.11.394 DMI.DMIVC1RCTL_0_0_0_DMIBAR     |       |

| 1.11.395 DMI.DMIVC1RSTS_0_0_0_DMIBAR     |       |

| 1.11.396 DMI.DMIVCECH_0_0_0_DMIBAR       |       |

| 1.11.397 DMI.DMIVCMNPRCA_0_0_0_DMIBAR    |       |

| 1.11.398 DMI.DMIVCMPRCA_0_0_0_DMIBAR     |       |

| 1.11.399 DMI.DMIVCMRCAP_0_0_0_DMIBAR     |       |

| 1.11.400 DMI.DMIVCMRCTL_0_0_0_DMIBAR     |       |

| 1.11.401 DMI.DMIVCMRSTS_0_0_0_DMIBAR     |       |

| 1.11.402 DMI.DMIVCPNPRCA_0_0_DMIBAR      |       |

| 1.11.403 DMI.DMIVCPPRCA_0_0_0_DMIBAR     |       |

| 1.11.404 DMI.DMIVCPRCAP_0_0_0_DMIBAR     |       |

| 1.11.405 DMI.DMIVCPRCTL_0_0_0_DMIBAR     |       |

| 1.11.406 DMI.DMIVCPRSTS_0_0_0_DMIBAR     |       |

| 1.11.407 DMI.ECOBNSTLLL_O_O_O_DMIBAR     |       |

| 1.11.408 DMI.ECOBNS_0_1_0_MMR            |       |

| 1.11.409 DMI.FCLKGTTLLL_0_0_0_DMIBAR     |       |

| 1.11.410 DMI.FUSESCMN_0_1_0_MMR          |       |

| 1.11.411 DMI.LOSLAT_0_0_0_DMIBAR         |       |

| 1.11.412 DMI.LCAP_0_0_0_DMIBAR           |       |

| 1.11.413 DMI.LCTL2_0_0_0_DMIBAR          |       |

| 1.11.414 DMI.LCTL_0_0_0_DMIBAR           |       |

| 1.11.415 DMI.LFSRSTS_0_1_0_MMR           |       |

| 1.11.416 DMI.LLTC_0_0_0_DMIBAR           |       |

| 1.11.417 DMI.LSTS2_0_1_0_PCI             |       |

| 1.11.418 DMI.LTSSMC_0_0_0_DMIBAR         |       |

| 1.11.419 DMI.NEGSTS_0_1_0_MMR            |       |

| 1.11.420 DMI.PCLKGTTLLL_O_O_O_DMIBAR     |       |

| 1.11.421 DMI.PEGBDWTHCHGTO_0_1_0_MMR     |       |

| 1.11.422 DMI.PEGCLKGTCMN_O_1_O_MMR       |       |

| 1.11.423 DMI.PEGCOMLCGCTRL_0_1_0_MMR     |       |

| 1.11.424 DMI.PEGINITLCGCTR_O_1_O_MMR     |       |

| 1.11.425 DMI.PEGLATFIXCTL_O_1_O_MMR      |       |

| 1.11.426 DMI.PEGSQSTAT_0_1_0_MMR         |       |

| 1.11.427 DMI.PEGTRANSLCGCTRL_0_1_0_MMR   |       |

| 1.11.428 DMI.PEGTST_0_1_0_MMR            |       |

| 1.11.429 DMI.PEGUPDNCFG_0_1_0_MMR        | 40U   |

| 1.11.431 DMI.PMONTLMASK_0_0_0_DMIBAR     |       |

| 1.11.432 DMI.PMTRLOS_0_1_0_MMR           |       |

| 1.11.433 DMI.PMTRL03_0_1_0_MMR           |       |

| 1.11.434 DMI.PSPC_0_1_0_MMR              |       |

| 1.11.435 DMI.PTHERMCTL_0_1_0_MMR         |       |

| 1.11.436 DMI.ROEO_0_1_0_MMR              |       |

| 1.11.437 DMI.SLOTSTS_0_1_0_PCI           |       |

| 1.11.438 DMI.THERMALCTRL_0_1_0_MMR       |       |

| 1.11.439 DMI.TOE0_0_1_0_MMR              |       |

| 1.11.440 DMI.TRNEN_0_1_0_MMR             |       |

| 1.11.441 DMI.UPCFGSTS_0_1_0_MMR          |       |

| 1.11.442 DMI.VC01CL_0_0_0_DMIBAR         |       |

| 1.11.443 DMI.VC01DATABUF_0_0_0_DMIBAR    |       |

| I.II.443DMI.VCOIDAIABUE () () () DIMIBAR | 4 / / |

| 1 11 14F DAIL VODACI, O. O. O. DAILDAD | 471         |

|----------------------------------------|-------------|

| 1.11.445 DMI.VCPMCL_0_0_0_DMIBAR       | 4/3         |

| 1.11.446 DMI.VCPMDATABUF_0_0_0_DMIBAR  | 474         |

| 1.11.447 DMI.VCPMTP_0_0_0_DMIBAR       |             |

| 1.11.448 DCAL                          | 475         |

| 1.11.449 DCO                           | 47 <i>6</i> |

| 1.11.450 DPMC0                         |             |

| 1.11.451 DPMC1                         |             |

| 1.11.452 DRMC                          |             |

| 1.11.453 DRP                           |             |

| 1.11.454 DTRO                          |             |

|                                        |             |

| 1.11.455 DTR1                          |             |

| 1.11.456DTR2                           |             |

| 1.11.457 DTR3                          |             |

| 1.11.458 DTRC                          |             |

| 1.11.459 PMSELO                        |             |

| 1.11.460 PMSEL1                        | 483         |

| 1.11.461 PMSEL2                        | 484         |

| 1.11.462 PMSEL3                        | 484         |

| 1.11.463 GVD.ASLE                      |             |

| 1.11.464 GVD.ASLS                      |             |

| 1.11.465 GVD.BSM                       |             |

| 1.11.466 GVD.CAPPOINT                  |             |

| 1.11.467 GVD.FD                        |             |

|                                        |             |

| 1.11.468GVD.GFX_IOBAR                  |             |

| 1.11.469 GVD.GMCH_PERF_EVTSEL0         |             |

| 1.11.470 GVD.GMCH_PERF_EVTSEL1         |             |

| 1.11.471 GVD.GMCH_PERF_EVTSEL2         |             |

| 1.11.472 GVD.GMCH_PERF_EVTSEL3         |             |

| 1.11.473 GVD.HDR                       |             |

| 1.11.474 GVD.ID                        |             |

| 1.11.475 GVD.INTR                      |             |

| 1.11.476 GVD.LBB                       | 490         |

| 1.11.477 GVD.MA                        | 490         |

| 1.11.478GVD.MANUFACTURING_ID           | 491         |

| 1.11.479 GVD.MD                        | 49          |

| 1.11.480 GVD.MGGC                      |             |

| 1.11.481 GVD.MMADR                     |             |

| 1.11.482 GVD.MMIO_DATA                 |             |

| 1.11.483 GVD.MMIO_INDEX                |             |

| 1.11.484 GVD.MSI_CAPID                 |             |

| 1.11.485 GVD.PCICMDSTS                 |             |

| 1.11.486 GVD.PMCAP                     |             |

|                                        |             |

| 1.11.487 GVD.PMCS                      |             |

| 1.11.488 GVD.RIDCC                     |             |

| 1.11.489 GVD.SSID                      |             |

| 1.11.490 GVD.SWSMISCI                  |             |

| 1.11.491 GVD.VC                        | 498         |

| 1.11.492 GVD.VCID                      | 499         |

| 1.11.493 HECREG                        | 499         |

| 1.11.494 HMBOUND                       | 500         |

| 1.11.495 HMBOUNDHI                     | 500         |

| 1.11.496 HMISC2                        |             |

| 1.11.497 HPOC                          |             |

| 1.11.498 HSMMCTL                       |             |

| 1.11.499 APM_CMD                       |             |

| 1 11 500 ΔPM IF                        | 500<br>509  |

| 1.11.501 APM_STS                                                              |      |

|-------------------------------------------------------------------------------|------|

| 1.11.502 C6C                                                                  |      |

| 1.11.503 CPU_RST                                                              |      |

| 1.11.504 DTELB                                                                | 506  |

| 1.11.505 DTELT                                                                |      |

| 1.11.506 GMCH_PERF_EVTSEL0                                                    | 507  |

| 1.11.507 GMCH_PERF_EVTSEL1                                                    | 508  |

| 1.11.508 GMCH_PERF_EVTSEL2                                                    | 508  |

| 1.11.509 GMCH_PERF_EVTSEL3                                                    | 509  |

| 1.11.510GTEL                                                                  | 509  |

| 1.11.511 LTEL                                                                 | 509  |

| 1.11.512LVL2                                                                  | 510  |

| 1.11.513LVL3                                                                  | 510  |

| 1.11.514LVL4                                                                  | 510  |

| 1.11.515LVL5                                                                  | 511  |

| 1.11.516LVL6                                                                  | 511  |

| 1.11.517 OSPMBA                                                               | 511  |

| 1.11.518 PCNT                                                                 | 512  |

| 1.11.519 PCR                                                                  | 512  |

| 1.11.520 PMBA                                                                 | 513  |

| 1.11.521 PM_CMD                                                               | 513  |

| 1.11.522 PM_ICS                                                               | 514  |

| 1.11.523 PM_SSC                                                               | 515  |

| 1.11.524 PM_SSS                                                               | 516  |

| 1.11.525 PM_STS                                                               | 518  |

| 1.11.526 TMA                                                                  | 518  |

| 1.11.527 TMC                                                                  | 518  |

| 1.11.528 TMD                                                                  | 519  |

| 1.11.529 TPSA                                                                 | 519  |

| 1.11.530 TPSTC                                                                |      |

| 1.11.531 TRR                                                                  | 520  |

| 1.11.532TSC                                                                   | 521  |

| 1.11.533 TSIS                                                                 |      |

| 1.11.534 TTB                                                                  |      |

| 1.11.535 TTR0                                                                 |      |

| 1.11.536 TTR1                                                                 |      |

| 1.11.537 TTS                                                                  |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Figure 1 1 Dhysical to DDAM Address Man                                       | 21   |

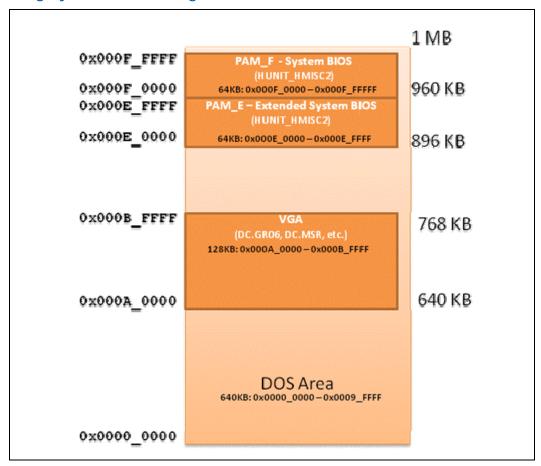

| Figure 1-1. Physical to DRAM Address Map                                      |      |

| Figure 1-2. Legacy DOS Address Range                                          |      |

| Figure 1-3.PCI MMIO Memory Address Range (HMBOUND – 4 GB)                     | . 33 |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| Table 1-1 Intel® Atom™ Processor D2000 series and N2000 Series Memory Mappir  | าต   |

| Registers                                                                     | _    |

| Table 1-2. Intel® Atom™ Processor D2000 series and N2000 Series Device 0 Memo |      |

| Map                                                                           | _    |

Table 1-3 Intel® Atom™ Processor D2000 series and N2000 Series Device 2 Memory

**Figures**

**Tables**

| Table 1-4. | IGD Frame Buffer Accesses | 29 |

|------------|---------------------------|----|

| Table 1-5. | IGD VGA I/O Mapping       | 29 |

# **Revision History**

| Revision<br>Number | Description                                                                                | Date           |

|--------------------|--------------------------------------------------------------------------------------------|----------------|

| 001                | Initial Release                                                                            | September 2011 |

| 002                | No updates for this volume in this release. Revision number updated to match with Volume 1 | December 2011  |

§

This is Volume 2 of the  $Intel @ Atom^{TM} Processor D2000 series and N2000 Series External Design Specification (EDS), and is intended to be distributed as part of the complete document. This document provides register information for the processor.$

#### 1.1 Related Documents

| Document Title                                                                             | Document<br>Number/<br>Location <sup>1</sup> |

|--------------------------------------------------------------------------------------------|----------------------------------------------|

| Intel® Atom™ Processor D2000 series and N2000 series External<br>Datasheet – Volume 1 of 2 | 326136                                       |

| Intel® Atom™ Processor D2000 Series and N2000 Series Specification Update                  | 326140                                       |

#### 1.2 Register Terminology

The following table shows the register-related terminology that is used in this document.

| Item  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RO    | Read Only bit(s). Writes to these bits have no effect. These are static values only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RO/P  | Read Only/Sticky bit(s). Writes to these bits have no effect. These are status bits only. Bits are not returned to their default values by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RS/WC | Read Set/Write Clear bit(s).  The first time the bit is read with an enabled byte, it returns the value 0, but a side-effect of the read is that the value changes to 1. Any subsequent reads with enabled bytes return a 1 until a 1 is written to the bit. When the bit is read, but the byte is not enabled, the state of the bit does not change, and the value returned is irrelevant, but will match the state of the bit.  When a 0 is written to the bit, there is no effect. When a 1 is written to the bit, its value becomes 0, until the next byte-enabled read. When the bit is written, but the byte is not enabled, there is no effect. |  |  |  |

| RW    | Read/Write bit(s). These bits can be read and written by software. Hardware may only change the state of this bit by reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| R/WC  | Read/Write Clear bit(s). These bits can be read. Internal events may set this bit. A software write of '1' clears (sets to '0') the corresponding bit(s) and a write of '0' has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Item    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/WC/L  | Read/Write Clear/Lockable bit(s). These bits can be read. Internal events may set this bit. A software write of '1' clears (sets to '0') the corresponding bit(s) and a write of '0' has no effect. Additionally there is a Key bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).                                                                                                                                                                                                                                                                                           |

| R/WC/P  | Read/Write Clear/Sticky bit(s). These bits can be read. Internal events may set this bit. A software write of '1' clears (sets to '0') the corresponding bit(s) and a write of '0' has no effect. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                                                                                                                                                                                                                    |

| R/W/B   | Read/Write/Blind bit(s). These bits can be read and written by software. Additionally there is a selector bit which, when set, changes what may be read from these bits. The value written is always stored in a hidden register. When the selector bit indicates that the written value should not be read, some other status is read from this bit. When the selector bit indicates that the written value should be read, the value in the hidden register is read from this bit.                                                                                                                                                                          |

| R/W/B/L | Read/Write/Blind/Lockable bit(s). These bits can be read and written by software. Additionally there is a selector bit which, when set, changes what may be read from these bits. The value written is always stored in a hidden register. When the selector bit indicates that the written value should not be read, some other status is read from this bit. When the selector bit indicates that the written value should be read, the value in the hidden register is read from this bit. Additionally there is a Key bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only). |

| R/W/K   | Read/Write/Key bit(s). These bits can be read and written by software.  Additionally this bit, when set, prohibits some other bit field(s) from being writeable (bit fields become Read Only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R/W/L   | Read/Write/Lockable bit(s). These bits can be read and written by software. Additionally there is a Key bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R/W/L/P | Read/Write/Lockable/Sticky bit(s). These bits can be read and written by software. Additionally there is a Key bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only). Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                                                                                                                                                                   |

| R/W/L/K | Read/Write/Lockable/Key bit(s). These bits can be read and written by software. Additionally this bit is a Key bit that, when set, prohibits this bit field and/or some other specified bit fields from being writeable (bit fields become Read Only).                                                                                                                                                                                                                                                                                                                                                                                                        |

| R/W/P   | Read/Write/Sticky bit(s). These bits can be read and written by software. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                                                                                                                                                                                                                                                                                                                                            |

| Item       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W/P/B    | Read/Write/Sticky/Blind bit(s). These bits can be read and written by software. Additionally there is a selector bit which, when set, changes what may be read from these bits. The value written is always stored in a hidden register. When the selector bit indicates that the written value should not be read, some other status is read from this bit. When the selector bit indicates that the written value should be read, the value in the hidden register is read from this bit. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec). |

| R/W/SC     | Read/Write/Self Clear bit(s). These bits can be read and written by software. When the bit is '1', hardware may clear the bit to '0' based upon internal events, possibly sooner than any subsequent software read could retrieve a '1'.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R/W/SC/L   | Read/Write/Self Clear/Lockable bit(s). These bits can be read and written by software. When the bit is '1', hardware may clear the bit to '0' based upon internal events, possibly sooner than any subsequent software read could retrieve a '1'. Additionally there is a bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only).                                                                                                                                                                                                                                                                        |

| R/W/SC/L/P | Read/Write/Self Clear/Lockable/Sticky bit(s). These bits can be read and written by software. When the bit is '1', hardware may clear the bit to '0' based upon internal events, possibly sooner than any subsequent software read could retrieve a '1'. Additionally there is a bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only). Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                        |

| R/W/SS/L/P | Read/Write/Self Set/Lockable/Sticky bit(s). These bits can be read and written by software. When the bit is '0', hardware may clear the bit to '1' based upon internal events, possibly sooner than any subsequent software read could retrieve a '0'. Additionally there is a bit (which is marked R/W/K or R/W/L/K) that, when set, prohibits this bit field from being writeable (bit field becomes Read Only). Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                          |

| R/WO       | Write Once bit(s). Once written by software, bits with this attribute become Read Only. These bits can only be cleared by a Reset. If there are multiple R/WO fields within a DWORD, they should be written all at once (atomically) to avoid capturing an incorrect value.                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/WO/P     | Write Once/Sticky bit(s). Once written by software, bits with this attribute become Read Only. These bits can only be cleared by a Reset. If there are multiple R/WO fields within a DWORD, they should be written all at once (atomically) to avoid capturing an incorrect value. Bits are not cleared by "warm" reset, but will be reset with a cold/complete reset (for PCI Express related bits a cold reset is "Power Good Reset" as defined in the PCI Express spec).                                                                                                                                                                                                          |

| W          | Write Only. These bits may be written by software, but will always return zeros when read. They are used for write side-effects. Any data written to these registers cannot be retrieved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R/W/1/0    | Write Logic 1 Once bit(s). Once written to logic 1 by software, bits with this attribute become Read Only. These bits can only be cleared by a Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 1.3 System Address Map

The Intel Atom Processor D2000 series and N2000 Series SoC supports 64GB (36 bit) of addressable memory space and 64 KB+3 of addressable I/O space. Addressing of greater than 4 GB is allowed on the DMI Interface as well as by the Intel Atom Processor D2000 series and N2000 Series GFX, Video, and Display units. The Intel Atom Processor D2000 series and N2000 Series SoC supports a maximum of 4GB of DRAM. There is no hardware lock to stop someone from inserting more memory than is addressable.

# 1.4 Intel Atom Processor D2000 series and N2000 Series Address Spaces

#### 1.4.1 Physical Address Space

This is the full 64GB (36bit) range of memory address space used by the CPU and devices. This is the address space accessible by memory reads, writes, and is the set of addresses as presented to the GMCH or devices from either the CPU or devices.

This address spaces has three sub-types depending on the final destination of the request and the mapping registers within CDV:

- Memory Mapped IO (MMIO) Ranges These are ranges in physical address space that accept loads/stores from the CPU and generally map those request to devices (registers or on-device memory) rather than system DRAM. These ranges must not be programmed to overlay each other. Request to these addresses ranges should only come from IA code (the CPU) and not from devices on Intel Atom Processor D2000 series and N2000 Series or from DMI

- **DRAM Ranges** These are ranges in physical address space that accept loads/stores from the CPU or Devices (both on Intel Atom Processor D2000 series and N2000 Series and from DMI) that map to System DRAM.

- Bad Memory Ranges These are ranges in physical address space that the BIOS must tag as unusable by the OS. This may be due to a lack of hardware support for the range or it may be that the range has been "stolen" for hardware private use.

Intel Atom Processor D2000 series and N2000 Series memory protection/security and coherency checking is performed in Physical Address Space. This includes IMRs, HMBOUND, HMBOUNDHI and ME UMA protection.

#### 1.4.2 System DRAM Address Space

This is the range of addresses presented to the memory controller after all security checks and reclaiming has been done. The memory controller is aware of the total amount of populated DRAM and addresses above this range are considered invalid – writes will be dropped and reads will return all 1's.

In truth, memory controllers including Intel Atom Processor D2000 series and N2000 Series have options to swizzle which System DRAM Address Space address bits map to banks, rows, columns to increase performance. For purposes of this discussion, this mapping is assumed to 1 to 1.

**System DRAM Stolen Memory Ranges** – These are portions of physical System DRAM held in reserved by Intel Atom Processor D2000 series and N2000 Series for internal purposes. The BIOS is responsible for not exposing these areas of DRAM to the Operating System and ensuring that stolen memory ranges don't overlap.

#### 1.4.3 **IO Space**

These are IO address ranges presented to the CPU. These are "IO" ranges in that they have a dedicated addressing space of 64KB+3 only accessible by the CPU using IN/OUT instructions. There is no relationship to memory space or PCI config space. These ranges must not be programmed to overlap each other. These requests never map to system DRAM and are not part of this discussion.

#### 1.4.4 PCI Config Space

PCI Config space is used to access many device register on and off CDV. This space is only accessible from the CPU. Intel Atom Processor D2000 series and N2000 Series converts special IN/OUT instructions from the CPU (or an optional MMIO Range) into PCI Config Space. Other than mentioning the MMIO range used for this, PCI Config Space is not part of this discussion.

#### 1.5 Physical to DRAM Address Space Mapping

Memory Mapping is defined has how Intel Atom Processor D2000 series and N2000 Series translates from Physical Address Space (as seen by the CPU and devices) to DRAM Address Space (as seen by the memory controller).

64<u>GB</u>

HMBOUND\_HIGH

Figure 1-1. Physical to DRAM Address Map

HIGH MMIO

Memory Controller Blocks Access Abové TOM High DRAM (Prevent Wrap Attack) Window 4.GB OS Visible **PCI MMIO** HMBOUND : BMBOUND Stolen Memory Unusable for MMIO Low DRAM Window OS Visible 1 MB DOS DRAM DOS DRAM

#### 1.5.1 Intel Atom Processor D2000 series and N2000 Series **Memory Mapping Registers**

Intel Atom Processor D2000 series and N2000 Series uses only two main registers to control this mapping: HMBOUND and HMBOUNDHI:

Table 1-1 Intel Atom Processor D2000 series and N2000 Series Memory Mapping Registers

TBD

#### 1.5.1.1 **HMBOUND**

This register sets a Physical Address Space location between 0 - 4GB. With few exceptions, request >= HMBOUND (but < 4GB) map to the device/DMI side if from the CPU and are rejected if from devices. Request < HMBOUND map to the memory controller with a 1:1 mapping from Physical Address Space to DRAM Address Space.

HMBOUND has a granularity of 256MB. It only matches the upper address bits and anything that matches or is greater will go to MMIO space. Since HMBOUND compares address bits [31:27], the highest physical it can be set is 0xF800\_0000h. Therefore, all address in 0xF8000\_0000h <= address < 0xFFFF\_FFFFh always map to PCI MMIO.

The DOS Legacy portion of Physical Address space is below HMBOUND, but has a few ranges than can be programmed to map to devices/DMI instead of System DRAM. These are covered later in this section.

Because systems generally need a 1-2 GBytes of Physical Address Space for MMIO, HMBOUND was typically set to a value such as 3GB (3GB available to the OS for DRAM, 1GB of address space available for MMIO). In order to avoid wasting any DRAM above 3GB, all Physical Addresses > 4GB are offset down such that the 4GB Physical Address Space address maps to the HMBOUND address in DRAM Address Space (4GB would map to 3GB in this example). This prevents wasting any DRAM.

#### 1.5.1.2 **HMBOUNDHI**

This register sets a Physical Address Space location between 4GB and 64GB.

Request < HMBOUNDHI (but >= 4GB) map to the memory controller but with a negative offset mapping from Physical Address Space to DRAM Address Space. This negative offset reclaims the portion of DRAM behind the PCI MMIO Range that would otherwise be unusable.

Request >= HMBOUNDHI from the CPU may to the device/DMI side for access to MMIO for 64bit devices. Request above HMBOUNDHI from devices attempt to map to the memory controller, but are rejected if above the amount of programmed DRAM.

HMBOUNDHI has a granularity of 4GB. This will often cause a HMBOUNDHI to be set higher than desired and a range of memory just below HMBOUNDHI will need to be set to "BAD" by the BIOS since it is unusable. See the programming examples.

# 1.6 Intel Atom Processor D2000 series and N2000 Series Memory Map Register Programming Examples

#### 1.6.1 Case 1: 2GB DRAM. Min 1 GB PCI MMIO

HMBOUND needs to be <= 3GB to make room for 1GB of PCI MMIO between HMBOUND and 4GB.

HMBOUND could be set to 3GB, but any Physical Address Space request from 2GB – 3GB will exceed available DRAM and this range will need to be marked as unavailable by the BIOS to the OS ("bad"). Instead, it's better to leave this 2GB – 3GB Physical Address Space range available for MMIO devices. Setting HMBOUND to 2GB makes all 2 GB of DRAM available and gives 2 GB of PCI MMIO space.

Since available DRAM is < 4GB, HMBOUNDHI should be set to 4GB, allowing all of the 4GB - 64GB address space to be used for 64bit PCI MMIO.

#### 1.7 Internal Device Memory Ranges

The Intel Atom Processor D2000 series and N2000 Series Address Map includes a number of programmable ranges for both Device 0 (Host) and Device 2 (GFX/Video/Display). The three main ranges discussed here are MMIO, Stolen DRAM, and IO Space. All are described in section Intel Atom Processor D2000 series and N2000 Series Address Spaces.

The rules for programming these ranges are:

- ALL of these ranges MUST be unique and NON-OVERLAPPING. It is the BIOS or system designers' responsibility to limit memory population so that adequate PCI, PCI Express, High BIOS, PCI Express Memory Mapped space, and APIC memory space can be allocated.

- Accesses to overlapped ranges may produce indeterminate results.

- In the case of overlapping ranges with memory, the memory decode will be given priority. This is a Intel® Trusted Execution Technology (Intel® TXT) requirement. It is necessary to get Intel TxT protection checks, avoiding potential attacks. Note that although the behavior conforms to Intel TxT requirement, the Intel TxT technology is NOT SUPPORTED in Intel Atom Processor D2000 series and N2000 Series.

- There are NO Hardware Interlocks to prevent problems in the case of overlapping ranges.